Optical Interconnection Design Innovator

# 400GbE to 400GbE (OSFP to OSFP) Direct Attach Cable P/N: GOS-PC401-XXC

#### **Features**

- ✓ Hot-plug OSFP form factor with close top heat sink

- ✓ Support 8x 50/Gb/s PAM4 modulation

- ✓ Commercial case temperature range of 0°C to 70°C

- √ 26 AWG ~30 AWG support up to 3m length

- ✓ Contain EEPROM & programmable to customized

#### **Applications**

- ✓ Data storage and communication industry

- ✓ Switch / router / HBA

- ✓ Enterprise network

- ✓ Data Center Network

- ✓ Infiniband

#### STANDARDS COMPLIANCE

- ✓ IEEE 802.3cd

- ✓ OSFP MSA HW Rev 4.1

- ✓ ROHS

#### **Description**

Gigalight's GOS-PC401-xxC cable assemblies are effective alternatives to fiber optics. The cable connects data signals from each of the 16 pairs on the single OSFP end to the other OSFP end, each pair operates at data rates of up to 50Gb/s, each OSFP port can be addressed by EEPROM to provide product information, which can be read or write by I2C interface.

Gigalight's GOS-PC401-xxC cable assemblies is compliant with the OSFP-MSA and IEEE 802.3cd, it's a high performance & cost effective I/O solutions for LAN, HPC and SAN. The high speed cable assemblies meet and exceed 800Gigabit Ethernet, InfiniBand EDR /HDR and temperature requirements for performance and reliability.

Optical Interconnection Design Innovator

# **Absolute Maximum Ratings**

| Parameter                  | Symbol         | Min | Max | Unit |

|----------------------------|----------------|-----|-----|------|

| Storage Temperature        | Ts             | -20 | 85  | °C   |

| Case Operating Temperature | T <sub>c</sub> | 0   | 70  | °C   |

| Humidity (non-condensing)  | Rh             | 5   | 95  | %    |

# **Recommended Operating Conditions**

| Parameter                  | Symbol         | Min | Typical | Max | Unit    |

|----------------------------|----------------|-----|---------|-----|---------|

| Operating Case Temperature | T <sub>c</sub> | 0   |         | 70  | °C      |

| Baud Rate per Lane (PAM4)  | fd             |     | 26.5625 |     | GBaud/s |

| Humidity                   | Rh             | 5   |         | 85  | %       |

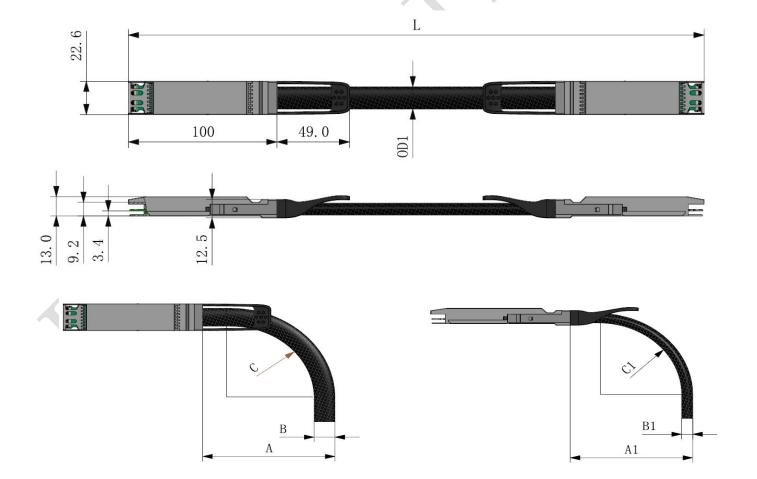

# **Mechanical Dimensions**

18-Oct-23 Rev. 0 2

Optical Interconnection Design Innovator

| OSFP Horizontal Direction |             |                       |                       |  |

|---------------------------|-------------|-----------------------|-----------------------|--|

| CABLE GUAGE               | DIAMETER"B" | MIN BEND<br>RADIUS"C" | MIN BEND<br>RADIUS"A" |  |

| 26AWG                     | 11MM        | 55MM                  | 65MM                  |  |

| OSFP Vertical Direction |              |                        |                        |  |

|-------------------------|--------------|------------------------|------------------------|--|

| CABLE GUAGE             | DIAMETER"B1" | MIN BEND<br>RADIUS"C1" | MIN BEND<br>RADIUS"A1" |  |

| 26AWG                   | 8MM          | 40MM                   | 50MM                   |  |

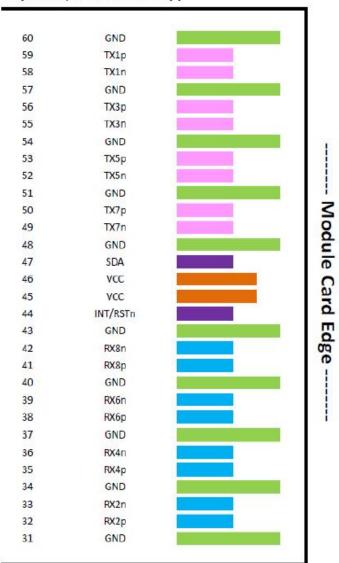

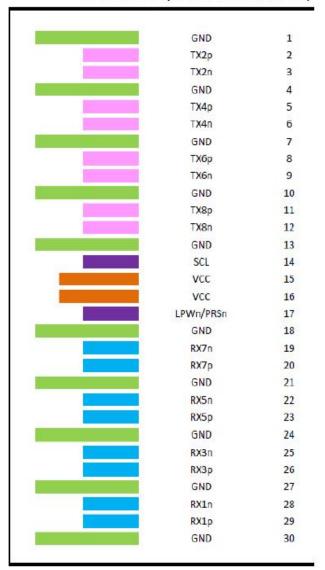

## **Electrical pinout**

Top Side (viewed from top)

# Bottom Side (viewed from bottom)

# Electrical pin list and description

18-Oct-23 Rev. 0 3

#### 深圳市易飞扬通信技术有限公司 Shenzhen Gigalight Technology Co., Ltd.

Optical Interconnection Design Innovator

|      |           |                                 | 1           |                 | Plug             |                                              |

|------|-----------|---------------------------------|-------------|-----------------|------------------|----------------------------------------------|

| Pin# | Symbol    | Description                     | Logic       | Direction       | Sequence         | Notes                                        |

| 1    | GND       | Ground                          |             |                 | 1                |                                              |

| 2    | TX2p      | Transmitter Data Non-Inverted   | CML-I       | Input from Host | 3                |                                              |

| 3    | TX2n      | Transmitter Data Inverted       | CML-I       | Input from Host | 3                |                                              |

| 4    | GND       | Ground                          |             | 23              | 1                |                                              |

| 5    | TX4p      | Transmitter Data Non-Inverted   | CML-I       | Input from Host | 3                |                                              |

| 6    | TX4n      | Transmitter Data Inverted       | CML-I       | Input from Host | 3                |                                              |

| 7    | GND       | Ground                          |             |                 | 1                |                                              |

| 8    | ТХ6р      | Transmitter Data Non-Inverted   | CML-I       | Input from Host | 3                |                                              |

| 9    | TX6n      | Transmitter Data Inverted       | CML-I       | Input from Host | 3                |                                              |

| 10   | GND       | Ground                          |             |                 | 1                |                                              |

| 11   | TX8p      | Transmitter Data Non-Inverted   | CML-I       | Input from Host | 3                |                                              |

| 12   | TX8n      | Transmitter Data Inverted       | CML-I       | Input from Host | 3                |                                              |

| 13   | GND       | Ground                          |             |                 | 1                |                                              |

| 14   | SCL       | 2-wire Serial interface clock   | LVCMOS-I/O  | Bi-directional  | 3                | Open-Drain with pull-<br>up resistor on Host |

| 15   | VCC       | +3.3V Power                     |             | Power from Host | 2                |                                              |

| 16   | VCC       | +3.3V Power                     |             | Power from Host | 2                |                                              |

| 17   | LPWn/PRSn | Low-Power Mode / Module Present | Multi-Level | Bi-directional  | 3                | See pin description<br>for required circuit  |

| 18   | GND       | Ground                          |             |                 | 1                |                                              |

| 19   | RX7n      | Receiver Data Inverted          | CML-O       | Output to Host  | 3                |                                              |

| 20   | RX7p      | Receiver Data Non-Inverted      | CML-O       | Output to Host  | 3                |                                              |

| 21   | GND       | Ground                          |             |                 | 1                |                                              |

| 22   | RX5n      | Receiver Data Inverted          | CML-O       | Output to Host  | 3                |                                              |

| 23   | RX5p      | Receiver Data Non-Inverted      | CML-O       | Output to Host  | 3                |                                              |

| 24   | GND       | Ground                          |             |                 | 1                |                                              |

| 25   | RX3n      | Receiver Data Inverted          | CML-O       | Output to Host  | 3                |                                              |

| 26   | RX3p      | Receiver Data Non-Inverted      | CML-O       | Output to Host  | 3                |                                              |

| 27   | GND       | Ground                          |             | -               | 1                |                                              |

| 28   | RX1n      | Receiver Data Inverted          | CML-O       | Output to Host  | 3                |                                              |

| 29   | RX1p      | Receiver Data Non-Inverted      | CML-O       | Output to Host  | 3                |                                              |

| 30   | GND       | Ground                          |             |                 | 1                |                                              |

| 31   | GND       | Ground                          |             |                 | 1                |                                              |

| 32   | RX2p      | Receiver Data Non-Inverted      | CML-O       | Output to Host  | 3                |                                              |

| in#  | Symbol    | Description                     | Logic       | Direction       | Plug<br>Sequence | Notes                                        |

| 33   | RX2n      | Receiver Data Inverted          | CML-O       | Output to Host  | 3                |                                              |

| 34   | GND       | Ground                          |             |                 | 1                |                                              |

| 35   | RX4p      | Receiver Data Non-Inverted      | CML-O       | Output to Host  | 3                |                                              |

| Pin# | Symbol   | Description                     | Logic       | Direction       | Plug<br>Sequence | Notes                                        |

|------|----------|---------------------------------|-------------|-----------------|------------------|----------------------------------------------|

| 33   | RX2n     | Receiver Data Inverted          | CML-O       | Output to Host  | 3                |                                              |

| 34   | GND      | Ground                          |             | 5               | 1                |                                              |

| 35   | RX4p     | Receiver Data Non-Inverted      | CML-O       | Output to Host  | 3                |                                              |

| 36   | RX4n     | Receiver Data Inverted          | CML-O       | Output to Host  | 3                |                                              |

| 37   | GND      | Ground                          |             |                 | 1                |                                              |

| 38   | RX6p     | Receiver Data Non-Inverted      | CML-O       | Output to Host  | 3                |                                              |

| 39   | RX6n     | Receiver Data Inverted          | CML-O       | Output to Host  | 3                |                                              |

| 40   | GND      | Ground                          |             |                 | 1                |                                              |

| 41   | RX8p     | Receiver Data Non-Inverted      | CML-O       | Output to Host  | 3                |                                              |

| 42   | RX8n     | Receiver Data Inverted          | CML-O       | Output to Host  | 3                |                                              |

| 43   | GND      | Ground                          |             |                 | 1                |                                              |

| 44   | INT/RSTn | Module Interrupt / Module Reset | Multi-Level | Bi-directional  | 3                | See pin description<br>for required circuit  |

| 45   | VCC      | +3.3V Power                     |             | Power from Host | 2                |                                              |

| 46   | vcc      | +3.3V Power                     |             | Power from Host | 2                |                                              |

| 47   | SDA      | 2-wire Serial interface data    | LVCMOS-I/O  | Bi-directional  | 3                | Open-Drain with pull-<br>up resistor on Host |

| 48   | GND      | Ground                          |             |                 | 1                |                                              |

| 49   | TX7n     | Transmitter Data Inverted       | CML-I       | Input from Host | 3                |                                              |

| 50   | ТХ7р     | Transmitter Data Non-Inverted   | CML-I       | Input from Host | 3                |                                              |

| 51   | GND      | Ground                          |             | 27              | 1                |                                              |

| 52   | TX5n     | Transmitter Data Inverted       | CML-I       | Input from Host | 3                |                                              |

| 53   | TX5p     | Transmitter Data Non-Inverted   | CML-I       | Input from Host | 3                |                                              |

| 54   | GND      | Ground                          |             |                 | 1                |                                              |

| 55   | TX3n     | Transmitter Data Inverted       | CML-I       | Input from Host | 3                |                                              |

| 56   | ТХЗр     | Transmitter Data Non-Inverted   | CML-I       | Input from Host | 3                |                                              |

| 57   | GND      | Ground                          |             |                 | 1                |                                              |

| 58   | TX1n     | Transmitter Data Inverted       | CML-I       | Input from Host | 3                |                                              |

| 59   | TX1p     | Transmitter Data Non-Inverted   | CML-I       | Input from Host | 3                |                                              |

| 60   | GND      | Ground                          |             |                 | 1                |                                              |

18-Oct-23 Rev. 0

Optical Interconnection Design Innovator

#### Ordering information

| Part Number      | GOS-PC401-XXC |       |    |  |

|------------------|---------------|-------|----|--|

| Length (meter)   | 1             | 2     | 3  |  |

| Wire gauge (AWG) | 30            | 30/26 | 26 |  |

If length(meter) is decimal, PN should be as GOS-PC401-DXXC.

## **Important Notice**

Performance figures, data and any illustrative material provided in this data sheet are typical and must be specifically confirmed in writing by Gigalight before they become applicable to any particular order or contract. In accordance with the Gigalight policy of continuous improvement specifications may change without notice.

The publication of information in this data sheet does not imply freedom from patent or other protective rights of Gigalight or others. Further details are available from any Gigalight sales representative.

E-mail: <a href="mailto:sales@gigalight.com">sales@gigalight.com</a>

Official Site: <a href="mailto:www.gigalight.com">www.gigalight.com</a>

### **Revision History**

| Revision | Date        | Description      |

|----------|-------------|------------------|

| V0       | Oct-18-2023 | Advance Release. |

18-Oct-23 Rev. 0 5