Optical Interconnection Design Innovator

# 25G DWDM SFP28 100GHz 10km Industrial **Optical Transceivers** GSS-Dxx250-LRT

#### **Features**

- Hot-pluggable SFP28 form factor

- Full-duplex transceiver module

- Cooled DWDM EML TOSA and APD ROSA

- Internal CDR on both transmitter and receiver channels

- Compliant with SFP28 MSA and CPRI/eCPRI specifications

- Data rate up to 25Gbps

- ITU-T G.694.1 DWDM frequency grid with 100GHz spacing

- Reach up to 10km over SMF

- Power consumption < 3.5W</li>

- Duplex LC receptacle

- Operating case temperature range -40°C to +85°C

- Single 3.3V power supply

- RoHS compliant (lead free)

# **Applications**

- 25G Ethernet

- CPRI Option 10

- eCPRI

### Description

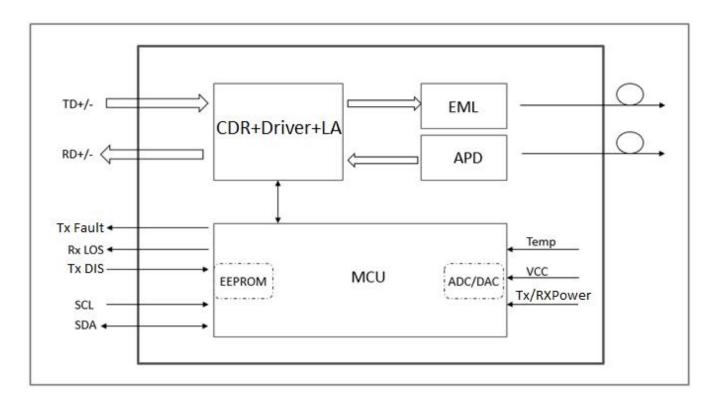

The Gigalight 25G DWDM SFP28 100GHz 10km industrial optical transceivers are designed for 25G Ethernet and CPRI/eCPRI links reach up to 10km over Single-Mode Fiber (SMF). Its high-performance cooled DWDM EML transmitter and high-sensitivity APD receiver provide superior performance for 4G/5G fronthaul applications.

Optical Interconnection Design Innovator

Figure 1. Module Block Diagram

The 25G DWDM SFP28 transceivers can be contacted through I<sup>2</sup>C system.

# **Absolute Maximum Ratings**

| Parameter                  | Symbol          | Min  | Max                  | Unit |

|----------------------------|-----------------|------|----------------------|------|

| Supply Voltage             | -0.3            | 3.6  | V                    |      |

| Input Voltage              | V <sub>in</sub> | -0.3 | V <sub>cc</sub> +0.3 | V    |

| Storage Temperature        | Ts              | -40  | 85                   | °C   |

| Case Operating Temperature | T <sub>c</sub>  | -40  | 85                   | °C   |

| Humidity (non-condensing)  | 0               | 85   | %                    |      |

# **Recommended Operating Conditions**

| Parameter                  | Symbol          | Min  | Typical | Max   | Unit |

|----------------------------|-----------------|------|---------|-------|------|

| Supply Voltage             | V <sub>cc</sub> | 3.13 | 3.3     | 3.47  | V    |

| Operating Case Temperature | T <sub>c</sub>  | -40  |         | 85    | °C   |

| Data Rate Per Lane         | fd              |      | 24.33   | 25.78 | Gb/s |

| Humidity                   | Rh              | 0    |         | 85    | %    |

| Power Dissipation          | P <sub>m</sub>  |      |         | 2     | W    |

| Fiber Bend Radius          | R <sub>b</sub>  | 3    |         |       | cm   |

in m.g.gangin.com

# **Electrical Specifications**

| Parameter                                          | Symbol           | Min                  | Typical | Max             | Unit  |

|----------------------------------------------------|------------------|----------------------|---------|-----------------|-------|

| Differential Input Impedance                       | Z <sub>in</sub>  | 90                   | 100     | 110             | ohm   |

| Differential Output Impedance                      | Z <sub>out</sub> | 90                   | 100     | 110             | ohm   |

| Differential Input Voltage Amplitude <sup>1</sup>  | $\Delta V_{in}$  | 300                  |         | 1100            | mVp-p |

| Differential Output Voltage Amplitude <sup>2</sup> | $\Delta V_{out}$ | 500                  |         | 800             | mVp-p |

| Skew                                               | Sw               |                      |         | 300             | ps    |

| Bit Error Rate                                     | BER              |                      | 5×10-5  |                 |       |

| Input Logic Level High                             | V <sub>IH</sub>  | 2.0                  |         | V <sub>cc</sub> | V     |

| Input Logic Level Low                              | V <sub>IL</sub>  | 0                    |         | 0.8             | V     |

| Output Logic Level High                            | V <sub>OH</sub>  | V <sub>cc</sub> -0.5 |         | V <sub>cc</sub> | V     |

| Output Logic Level Low                             | V <sub>OL</sub>  | 0                    |         | 0.4             | V     |

### **Notes:**

- 1. Differential input voltage amplitude is measured between TxnP and TxnN.

- 2. Differential output voltage amplitude is measured between RxnP and RxnN.

# **Optical Characteristics**

| Parameter                                                                                     | Symbol           | Min                | Typical | Max   | Unit  |

|-----------------------------------------------------------------------------------------------|------------------|--------------------|---------|-------|-------|

| Tra                                                                                           | nsmitter         |                    |         |       |       |

| Optical Wavelength                                                                            | λс               | As per ITU-T 694.1 |         |       | nm    |

| Side-Mode Suppression Ratio                                                                   | SMSR             | 30                 |         |       | dB    |

| Average Launch Power                                                                          | P <sub>out</sub> | 0                  |         | 4     | dBm   |

| Optical Modulation Amplitude                                                                  | OMA              | 0                  |         | 4     | dBm   |

| Extinction Ratio                                                                              | ER               | 3                  |         |       | dB    |

| Average Launch Power of OFF Transmitter                                                       | P <sub>off</sub> |                    |         | -30   | dB    |

| Rin <sub>20</sub> OMA                                                                         |                  |                    |         | -130  | dB/HZ |

| Optical return loss tolerance                                                                 |                  |                    |         | 20    | dB    |

| Eye Mask Coordinates <sup>1</sup> : X1, X2, X3, Y1, Y2, Y3 {0.31, 0.4, 0.45, 0.34, 0.38, 0.4} |                  |                    |         |       |       |

| R                                                                                             | eceiver          |                    |         |       |       |

| Center Wavelength                                                                             | λ <sub>c</sub>   | 1260               |         | 1600  | nm    |

| Receiver Sensitivity in OMA <sup>2</sup>                                                      |                  |                    |         | -19   | dBm   |

| Stressed Receiver Sensitivity in OMA <sup>2</sup>                                             |                  |                    |         | -16.5 | dBm   |

| Average Power at Receiver Input (each lane)                                                   |                  | -27                |         | -5    | dBm   |

| Receiver Reflectance                                                                          | R <sub>R</sub>   |                    |         | -26   | dB    |

| LOS Assert                                                                                    | LOSA             | -30                |         |       | dBm   |

| LOS De-Assert – OMA                                                                           | LOS <sub>D</sub> |                    |         | -17   | dBm   |

| LOS Hysteresis                                                                                | LOS <sub>H</sub> | 0.5                |         |       | dB    |

#### **Notes:**

www.gigalight.com

Optical Interconnection Design Innovator

- 1. Hit Ratio =  $5 \times 10^{-5}$

- 2. Measured with conformance test signal at TP3 for BER= $10^{-5}$

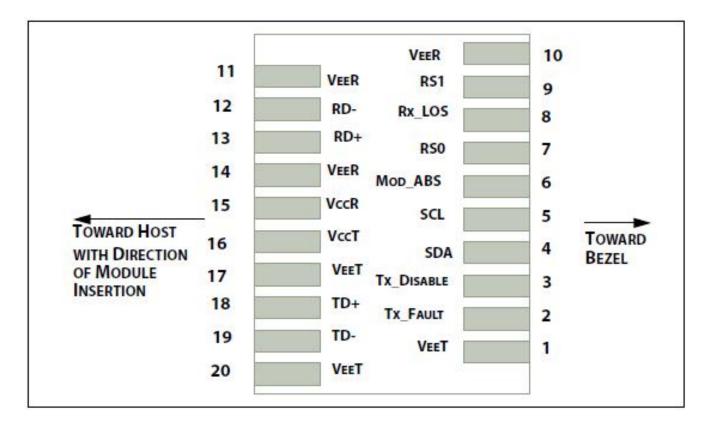

# **Pin Description**

| Pin | Logic     | Symbol   | Name/Description                                        |   |

|-----|-----------|----------|---------------------------------------------------------|---|

| 1   |           | VeeT     | Module Transmitter Ground                               | 1 |

| 2   | LVTTL-O   | TX_Fault | Module Transmitter Fault                                | 2 |

| 3   | LVTTL-I   | TX_Dis   | Transmitter Disable; Turns off transmitter laser output |   |

| 4   | LVTTL-I/O | SDA      | 2-Wire Serial Interface Data Line                       | 2 |

| 5   | LVTTL-I   | SCL      | 2-Wire Serial Interface Clock                           | 2 |

| 6   |           | MOD_ABS  | Module Definition, Grounded in the module               |   |

| 7   | LVTTL-I   | RS0      | Receiver Rate Select                                    |   |

| 8   | LVTTL-O   | RX_LOS   | Receiver Loss of Signal Indication Active LOW           |   |

| 9   | LVTTL-I   | RS1      | Transmitter Rate Select (not used)                      |   |

| 10  |           | VeeR     | Module Receiver Ground                                  | 1 |

| 11  |           | VeeR     | Module Receiver Ground                                  | 1 |

| 12  | CML-O     | RD-      | Receiver Inverted Data Output                           |   |

| 13  | CML-O     | RD+      | Receiver Data Output                                    |   |

| 14  |           | VeeR     | Module Receiver Ground                                  | 1 |

| 15  |           | VccR     | Module Receiver 3.3 V Supply                            |   |

| 16  |           | VccT     | Module Receiver 3.3 V Supply                            |   |

| 17  |           | VeeT     | Module Transmitter Ground                               | 1 |

| 18  | CML-I     | TD+      | Transmitter Non-Inverted Data Input                     |   |

| 19  | CML-I     | TD-      | Transmitter Inverted Data Input                         |   |

| 20  |           | VeeT     | Module Transmitter Ground                               | 1 |

### **Notes:**

- 1. Module ground pins GND are isolated from the module case.

- 2. Shall be pulled up with 4.7K-10K ohms to a voltage between 3.15V and 3.45V on the host board.

Figure 2. Electrical Pin-out Details

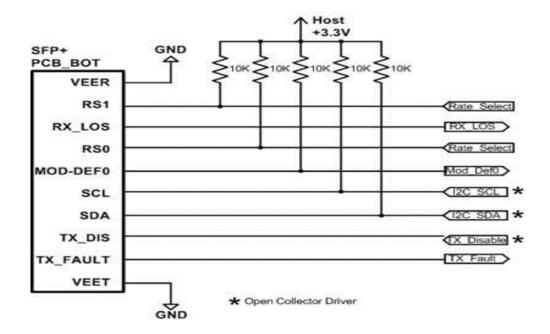

#### TX\_FAULT Pin

Tx\_Fault is a module output that when high, indicates that the module transmitter has detected a fault condition related to laser operation or safety. The Tx\_Fault output is an open drain/collector and shall be pulled up to the Vcc\_Host in the host with a resistor in the range 4.7 k $\Omega$  to 10 k $\Omega$ .

### TX\_DISABLE Pin

When Tx\_Disable is asserted high or left open, the SFP+ module transmitter output shall be turned off unless the module is a passive cable assembly. This contact shall be pulled up to VccT with a 4.7  $k\Omega$  to 10  $k\Omega$  resistor in modules and cable assemblies.Tx\_Disable is a module input contact.

#### RS0/RS1 Pin

RSO and RSI are module inputs and are pulled low to VeeT with > 30 k $\Omega$  resistors in the module. RSO optionally selects the optical receive signaling rate coverage. RSI optionally selects the optical transmit signaling rate coverage.

#### MOD\_ABS Pin

Mod\_ABS is connected to VeeT or VeeR in the SFP+ module. The host may pull this contact up to Vcc\_Host with a resistor in the range 4.7 k $\Omega$  to10 k $\Omega$ .Mod\_ABS is asserted "High" when the SFP+ module is physically absent from a host slot. In the SFP MSA (INF-8074i) this contact has the same function but is called MOD\_DEFO.

Optical Interconnection Design Innovator

Gigalight

#### **RX LOS Pin**

Rx\_LOS when high indicates an optical signal level below that specified in the relevant standard. Rx\_LOS is an open drain/collector output, but may also be used as an input by supervisory circuitry in the module. For a nominally 3.3 V Vcc\_Host using a resistive pull up to Vcc\_Host the resistor value shall be in the range 4.7 k $\Omega$  to 10 k $\Omega$ . For a nominally 2.5 V Vcc\_Host using a resistive pull up to Vcc\_Host the resistor value shall be in the range 4.7 k $\Omega$  to 7.2 k $\Omega$ .

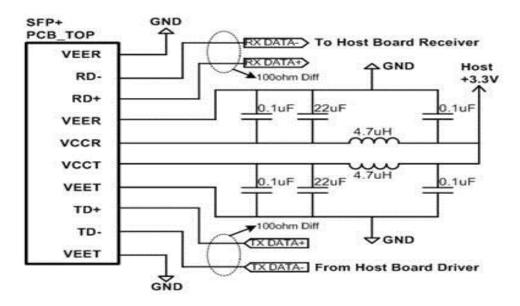

#### **Recommended Interface Circuit**

Figure 3. Recommended Interface Circuit

www.gigalight.com

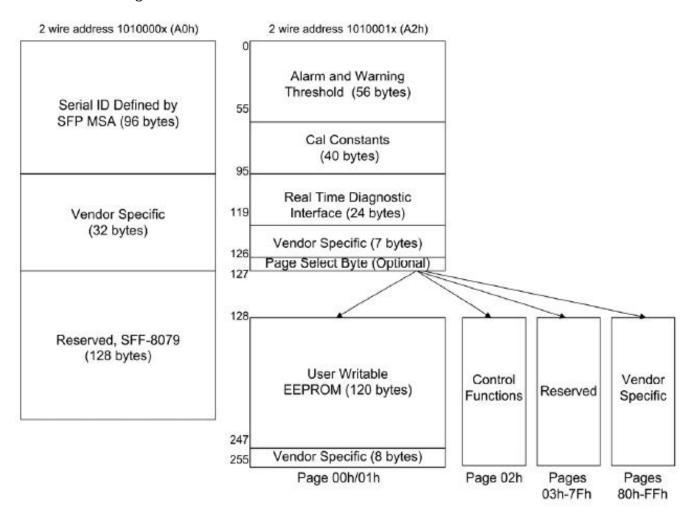

### **Memory Organization**

The transceivers provide serial ID memory contents and diagnostic information about the present operating conditions by the 2-wire serial interface (SCL, SDA). The memory map specific data field defines as following.

Figure 5. SFP28 Memory Map

www.gigalight.com

# **Timing and Electrical**

| Parameter                                                                                     | Symbol                | Min. | Max. | Unit | Conditions                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------|-----------------------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tx_Disable assert time                                                                        | t_off                 |      | 100  | μѕ   | Rising edge of Tx_Disable to fall of output signal<br>below 10% of nominal                                                                                                                                                                                                                                                                      |

| Tx_Disable negate time                                                                        | t_on                  |      | 2    | ms   | Falling edge of Tx_Disable to rise of output signal<br>above 90% of nominal. This only applies in normal<br>operation, not during start up or fault recovery.                                                                                                                                                                                   |

| Time to initialize 2-wire interface                                                           | t_2w_start_up         |      | 300  | ms   | From power on or hot plug after the supply meeting <u>Table 8</u> .                                                                                                                                                                                                                                                                             |

| Time to initialize                                                                            | t_start_up            |      | 300  | ms   | From power supplies meeting <u>Table 8</u> or hot plug or Tx disable negated during power up, or Tx_Fault recovery, until non-cooled power level I part (or non-cooled power level II part already enabled at power level II for Tx_Fault recovery) is fully operational.                                                                       |

| Time to initialize cooled module<br>and time to power up a cooled<br>module to Power Level II | t_start_up_cooled     |      | 90   | 5    | From power supplies meeting <u>Table 8</u> or hot plug, or Tx disable negated during power up or Tx_Fault recovery, until cooled power level I part (or cooled power level II part during fault recovery) is fully operational. Also, from stop bit low-to-high SDA transition enabling Power Level II until cooled module is fully operational |

| Time to Power Up to Level II                                                                  | t_power_level2        |      | 300  | ms   | From stop bit low-to-high SDA transition enabling<br>power level II until non-cooled module is fully<br>operational                                                                                                                                                                                                                             |

| Time to Power Down from Level II                                                              | t_power_down          |      | 300  | ms   | From stop bit low-to-high SDA transition dis-<br>abling power level II until module is within power<br>level I requirements                                                                                                                                                                                                                     |

| Tx_Fault assert                                                                               | Tx_Fault_on           |      | 1    | ms   | From occurrence of fault to assertion of Tx_Fault                                                                                                                                                                                                                                                                                               |

| Tx_Fault assert for cooled module                                                             | Tx_Fault_on_cooled    |      | 50   | ms   | From occurrence of fault to assertion of Tx_Fault                                                                                                                                                                                                                                                                                               |

| Tx_Fault Reset                                                                                | t_reset               | 10   |      | μs   | Time Tx_Disable must be held high to reset Tx_Fault                                                                                                                                                                                                                                                                                             |

| RS0, RS1 rate select timing for FC                                                            | t_RS0_FC,<br>t_RS1_FC |      | 500  | μs   | From assertion till stable output                                                                                                                                                                                                                                                                                                               |

| RS0, RS1 rate select timing non FC                                                            | t_RS0, t_RS1          |      | 24   | ms   | From assertion till stable output                                                                                                                                                                                                                                                                                                               |

| Rx_LOS assert delay                                                                           | t_los_on              |      | 100  | μs   | From occurrence of loss of signal to assertion of Rx_LOS                                                                                                                                                                                                                                                                                        |

| Rx_LOS negate delay                                                                           | t_los_off             |      | 100  | μs   | From occurrence of presence of signal to negation of Rx_LOS                                                                                                                                                                                                                                                                                     |

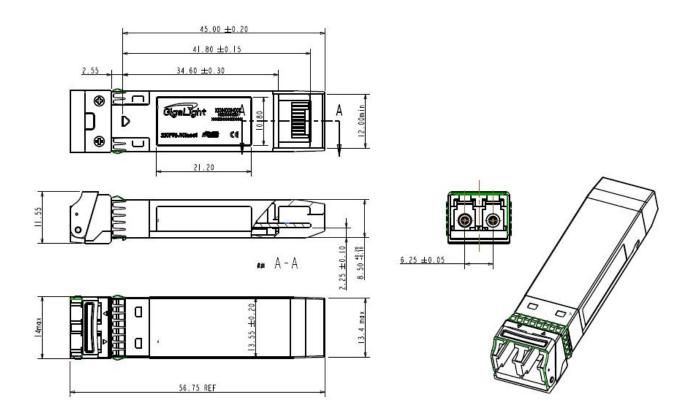

# **Mechanical Dimensions**

**Figure 6. Mechanical Specifications**

# **Regulatory Compliance**

The Gigaligth GSS-Dxx250-LRT transceivers are Class 1 Laser products. They are certified per the following standards:

| snownig standards.       |                                                                        |  |  |  |

|--------------------------|------------------------------------------------------------------------|--|--|--|

| Feature                  | Standard                                                               |  |  |  |

| Laser Safety             | IEC 60825-1:2014 (Third Edition)                                       |  |  |  |

| Environmental protection | 2011/65/EU                                                             |  |  |  |

| CE EMC                   | EN55032: 2015<br>EN55035: 2017<br>EN61000-3-2:2014<br>EN61000-3-3:2013 |  |  |  |

| FCC                      | FCC Part 15, Subpart B; ANSI C63.4-2014                                |  |  |  |

### References

- 1. SFP28 MSA

- 2. Ethernet IEEE 802.3cc

- 3. Directive 2011/65/EU of the European Parliament and of the Council, "on the restriction of the use

#### 深圳市易飞扬通信技术有限公司 Shenzhen Gigalight Technology Co., Ltd.

Optical Interconnection Design Innovator

of certain hazardous substances in electrical and electronic equipment," July 1, 2011.

Use of controls or adjustment or performance of procedures other than those specified herein may result in hazardous radiation exposure.

## **Ordering Information**

www.gigalight.com

| Part Number                                        | Product Description                                        |  |  |  |

|----------------------------------------------------|------------------------------------------------------------|--|--|--|

| GSS-Dxx250-LRT                                     | 25G DWDM SFP28 100GHz 10km Industrial Optical Transceivers |  |  |  |

| The xx means the wavelength options from 17 to 61. |                                                            |  |  |  |

### **Important Notice**

Performance figures, data and any illustrative material provided in this data sheet are typical and must be specifically confirmed in writing by Gigalight before they become applicable to any particular order or contract. In accordance with the Gigalight policy of continuous improvement specifications may change without notice.

The publication of information in this data sheet does not imply freedom from patent or other protective rights of Gigalight or others. Further details are available from any Gigalight sales representative.

E-mail: <a href="mailto:sales@gigalight.com">sales@gigalight.com</a>

Official Site: <a href="mailto:www.gigalight.com">www.gigalight.com</a>

### **Revision History**

| Revision | Date        | Description      |

|----------|-------------|------------------|

| VO       | May-07-2019 | Advance Release. |